The MMU is responsible of performing virtual to physical memory address translation as well as permission checking for every memory access done by the CPU core. The Translation Lookaside Buffer or TLB for short is a specialized cache used by modern processors that have a Memory Management Unit (MMU). It’s this worst case that we are trying to improve. Most importantly, however, is the worst case, which is far to the right at 1778 cycles and very infrequent, happening once in 2 million iterations. The overall response time is rather good, an average of 876 cycles and the fastest response time at 154 cycles. The distribution is relatively wide and bell shaped, which isn’t surprising considering the random nature of the input. Figure 1 – Interrupt latency distribution, no lockdown. This is the result of 2 million iterations without any lockdown. The results would be very similar with an efficient RTOS.

CACHE COHERENCE CORTEX A9 CODE

Everything is done with a minimal bare metal environment to minimize the effect of code and data outside of our interests. This method of measuring interrupt latency is explained in details in another article.

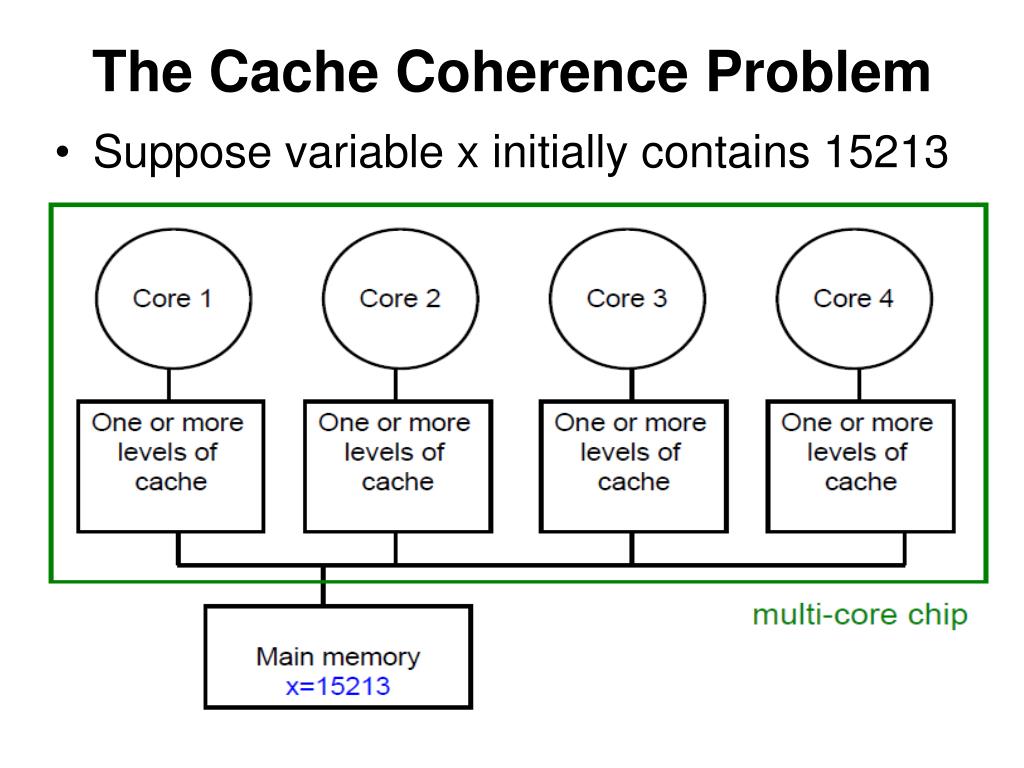

Measuring the time between the trigger and the interrupts gives a distribution of interrupt latency. The test is relatively simple and consists of performing a random number of (random) data and instruction accesses and then triggering an interrupt. However, in this article, I’ll attempt to demonstrate how it works and what can be achieved using a synthetic workload. Worst case interrupt latency is very application specific and consequently, the effect of cache lockdown depends a lot on the application layout and memory access patterns. When asked about those features, and if they can help improve interrupt latency in a customer’s application, it’s often hard to put numbers to back the discussion. TLB lockdown, on the other hand, prevents TLB misses on those same areas. In theory, cache lockdown or isolation, prevents other data and instructions from taking the place of critical code and data. However, the Cortex-A9 is still a popular core, found on the Xilinx Zynq-7000 and NXP i.MX 6 SoCs to name a few. Newer cores have a simpler TLB, and most often than not an integrated L2 cache instead of the external L2 found on the A9.

CACHE COHERENCE CORTEX A9 64 BITS

It’s important to note that those two features are not available in more recent 32 and 64 bits ARM processors such as the Cortex-A7. Namely the L2 cache and TLB lockdown features found in those processors.

CACHE COHERENCE CORTEX A9 DRIVERS

With up to 6.6M logic cells and offered with transceivers ranging from 6.25Gb/s to 12.5Gb/s, Zynq 7000 devices enable highly differentiated designs for a wide range of embedded applications including multi-camera drivers assistance systems and 4K2K Ultra-HDTV.Continuing from the last post, this article explores features specific to early members of the ARM Cortex-A family such as the Cortex-A9. Zynq 7000 devices are equipped with dual-core ARM Cortex-A9 processors integrated with 28nm Artix 7 or Kintex™ 7 based programmable logic for excellent performance-per-watt and maximum design flexibility. Available with 6.25Gb/s transceivers and outfitted with commonly used hardened peripherals, the Zynq 7000S delivers cost-optimized system integration ideal for industrial IoT applications such as motor control and embedded vision.

Zynq 7000S devices feature a single-core ARM Cortex®-A9 processor mated with 28nm Artix™ 7 based programmable logic, representing a low cost entry point to the scalable Zynq 7000 platform.

0 kommentar(er)

0 kommentar(er)